MCS-51单片机与FPGA

1 单片机 单片机是单片微型计算机(Single-Chip Microcomputer)的简称,是一种将中心处理器微处理器随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计时器等功能(可能还包括显示驱动电路、脉宽调制电路、模拟多路转换器、A/D转换器等电路)采纳超大规模集成电路技术集成到一块硅片上构成的微型计算机系统。 [全文] 现场可编程逻辑门阵列(FPGA, Field Programmable Gate Array),是一个含有可编辑元件的半导体设备,可供使用者现场程式化的逻辑门阵列元件。FPGA是在PAL、GAL、CPLD等可编辑器件的基础上进一步进展的产物。 [全文] 单片机

单片机 FPGA

FPGA

单片机与FPGA的接口方式一般有两种,即总线 总线

总线

总线是将信息以一个或多个源部件传送到一个或多个目的部件的一组传输线。通俗的说,就是多个部件间的公共连线,用于在各个部件之间传输信息。人们经常以MHz表示的速度来描述总线频率。 [全文]

方式与独立方式。MCS-51单片机 51单片机

51单片机51单片机是单片机中的一种,单片机(single-chip microcomputer)是一块集成芯片,但不是一块实现某一个逻辑功能的芯片,而是在这块芯片当中,集成了一个计算机系统。如中心处理器(微处理器)、存储器(ROM,RAM)、I/O接口、定时器/计数器、中断系统等。中心处理器是单片机的核心单元,他由运算器和操纵器组成,他的主要功能是实现算术运算、逻辑运算、和操纵。 [全文]

具有很强的外部总线扩展能力,利用片外三总线结构很轻易实现单片机与FPGA的总线接口,而且单片机以总线方式与FPGA进行数据与操纵信息通信也有许多优点:速度快;节省PLD芯片的I/O口线;相对于非总线方式,单片机编程简捷,操纵可靠;在FPGA中通过逻辑切换,单片机易于与SRAM或ROM接口。单片机与FPGA以总线方式通信的逻辑设计,重要的是要具体了解单片机的总线读写时序,根据时序图来设计逻辑结构,其通信的时序必须遵循单片机内固定的总线方式读/写时序。FPGA的逻辑设计也相对比较复杂,在程序设计上必须与接口的单片机程序相结合,严格安排单片机能访问的I/O空间。单片机以总线方式与FPGA进行数据通信与操纵时,其通信工作时序是纯硬件行为,速度要比前一种方式快得多,另外若在FPGA内部设置足够的译码输出,单片机就可以仅通过19根I/O线在FPGA与单片机之间进行通信和操纵信息交换,这样可以节省FPGA芯片的I/O线。其原理图如图1所示。

2 总线接口逻辑设计

2.1 接口设计思想

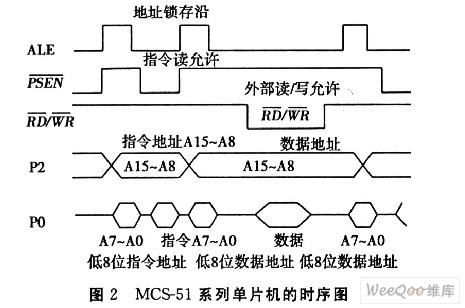

单片机与CPLD/FPC,A以总线方式通信的逻辑设计,重要的是要具体了解单片机的总线读写时序,根据时序图来设计逻辑结构。MCS-51系列单片机的时序图如图2所示。

ALE为地址锁存使能信号,可利用其下降沿将低8位地址锁存于FPGA中的地址锁存器(LATCH_ADDRES)中;当ALE将低8位地址通过P0锁存的同时,高8位地址已稳定建立于P2口,单片机利用读指令同意信号PSEN的低电平从外部ROM中将指令从P0口读入,由时序图可见,其指令读入的时机是在PSEN的上升沿之前。接下来,由P2口和P0口分别输出高8位和低8位数据地址,并由ALE的下降沿将P0口的低8位地址锁存于地址锁存器。若需从FPGA中读出数据,单片机则通过指令“MOVXA,@DPTR”使RD信号为低电平,由P0口将锁存器中的数据读入累加器A;但若欲将累加器A的数据写进FPGA,则需通过指令“MOVx DPTR,A”和写同意信号WR。这时,DPTR中的高8位和低8位数据作为高、低8位地址分别向P2和P0口输出,然后由WR的低电平并结合译码,将累加器A的数据写入图中相关的锁存器。

通过对MCS-51单片机总线读/写时序的分析,设计了图3所示的接口电路。在FPGA中,设计了两个模块:一个是总线接口模块,负责单片机与FPGA的总线接口逻辑;另一个是寄存器单元及外部接口模块,运用总线接口模块来操作此模块。

在总线应用时,MCS-51单片机的P0口是作为地址/数据总线分时复用的,因此应在总线接口模块中设计一个三态缓冲器 缓冲器

缓冲器

缓冲器是种保持加、卸试验力平稳,或减缓试样断裂时冲击的装置。它可以弥补不同数据处理速率速度差距,也可以起到缓冲避震作用,及起到实现数据传送同步的作用等。它涉及的领域非常广泛,有电信设备、数控处理、生化科技、系统安全等。它在不同的领域有着不同的名称,其中常见的有寄存缓冲器、汽车弹簧缓冲器(缓冲胶)、电梯缓冲器等。它分常用缓冲器(常说缓冲器)和三态缓冲器。 [全文]

,实现P0口的三态接口;又因MCS-51单片机在访问外部空间时,它的地址为16位,因此借助地址锁存使能信号ALE在FPGA中实现高8位与低8位地址的编码,组合成16位地址,然后再根据MCS-51单片机的读/写信号,实现对FPGA的读写操作。在接口设计中,采纳了VHDL语言实现其接口逻辑。用VHDL语言编写,往往比较方便和严谨,注重整个过程的逻辑思路,并且尽量幸免语言的冗余,造成比较长的延时。-MCS-51单片机与FPGA的通信读写电路的部分程序

FPGA是一种新兴的可编程逻辑器件,可以取代现有的全部微机接口芯片,实现微机系统中的存储器 存储器

存储器

存储器是用来存储程序和数据的部件,有了存储器,计算机才有记忆功能,才能保证正常工作。它根据操纵器指定的位置存进和取出信息。 [全文]

、地址译码等多种功能,具有更高的密度、更快的工作速度和更大的编程灵活性,被广泛应用于各种电子类产品中。在功能上,单片机具有性价比高、功能灵活、易于人机对话、强大的数据处理能力等特点;而FPGA则具有高速、高可靠性以及开发便捷、规范等特点,因此两类器件相结合的电路结构将在许多高性能仪器仪表 仪器仪表

仪器仪表广义的说仪器仪表也可具有自动操纵、报警、信号传递和数据处理等功能,如气动调节仪、电动调节仪表,以及集散型仪表操纵系统等也皆属器仪表。仪器仪表能改善、扩展或补充人的官能。如显微镜、望远镜、声级计、酸度计、高温计等,可以扩展人的视、听、尝、摸外部事物的官能;有些仪器仪表,如磁强计、射线计数计等,可感受和测试到人所不能感受到的物理量;还有些仪器仪表可以超过人的能力去记录、计算和计数,如高速照相机、计算机等。 [全文]

和电子产品中被广泛应用。基于这种需求,本文设计了MCS-51单片机与FPGA的总线接口逻辑电路 逻辑电路

逻辑电路逻辑电路是包含逻辑关系的数字电路, 以二进制为原理、实现数字离散信号的传递,逻辑运算和操作的电路。最基本的逻辑电路是常见的门电路,而最简洁的门电路为与电路、或电路和非电路。 [全文]

,实现了单片机与FPGA数据与操纵信息的可靠通信,使FP―GA与单片机优势互补,组成灵活的、软硬件都可现场编程的操纵系统。来源:1111光棍

该文章来至网络或用户,仅供学习交流之用,版权归原作者所有。

如有侵权,请及时与我们联系!

基于MCS-51单片机的断相与相序守护系统的设计

摘 要:本文介绍了一种简洁有用的数字式断相与相序守护技术的原理,给出了基于MCS―51单片机的断相与相序守护数字操纵系统的硬件电路及简洁软件介绍,实现了三相交流操纵...

MCS-51单片机外中断软件编程

MCS-51单片机有多个中断源,以8051为例,有5个中断源,两个外中断、两个定时中断和一个串行中断,这一节我们讨论外中断软件编程。 外中断是由外部缘由引起的中断,有两...

MCS-51单片机主要应用特性

MCS-51单片机是美国INTE公司于1980年推出的产品,与MCS-48单片机相比,它的结构更先进,功能更强,在原来的基础上增加了更多的电路单元和指令,指令数达111条,MCS-51单片机...

MCS-51单片机的指令时序

时序是用定时单位来描述的,MCS-51的时序单位有四个,它们分别是节拍、状态、机器周期和指令周期,接下来我们分别加以说明。 ・节拍与状态: 我们把振荡脉冲...

基于MCS-51单片机的智能时钟操纵系统设计的技巧

随着电子技术产业结构调整,生产工艺的飞速进展,人们生活水平的不断提高,家用电器逐渐普及,市场对于智能时钟操纵系统的需求也越来越大。本文所述智能时钟操纵系统主要指...